从零理解 STM32 系统初始化与中断配置 (NVIC) 机制

刚接触 STM32 及标准库(或者 HAL 库底层的逻辑)时,一定会惊讶于一段看似冗长且重复的“点灯”前置代码。 本文尝试为你拆解那最为关键的系统级初始化流,让你明白:到底我们是在图些什么?如果不写这些代码会发生什么严重的后果?

必须要做的第一步:系统时钟开启

你在 main 函数的最顶端,一定会看到如下面目可憎的系统配置语句:

SystemClock_Config(); // 或是自己手写配置 RCC 的函数它能让开发板完成最华丽的“起搏心跳”。如果不经过它的手,整个单片机充其量只是块低耗能的“死硅片”。

单片机的上电节拍策略

不像个人电脑 PC 上电后主板立刻会让 CPU 与内存飙到最高的预设频率,大多数单片机出于节能安全考虑,在复位上电的一瞬间,它们的时钟默认是完全关闭的,或者仅仅启用了极其懒散的内部低速时钟 (例如 8MHz / 16MHz)。 如果不做初始化:

- 单片机将只能慢吞吞地执行 8M 频率的任务(对于能冲刺 72M/168M 频率的它来说太过浪费)。

- 基于严格时间切片运作的外设将无法协同。串口波特率发生错乱,变成电脑端的乱码;ADC 定时采样失败;你的

HAL_Delay(1000)可能一口气卡上 10 秒钟。

为什么低频率起手被视为一种安全机制?

试想如果你挂载的外部晶振 (HSE) 在焊接出厂时发生了物理损坏,或者起振电容选配不当。 如果一上电就硬锁外部高速时钟,电路很可能当场因无法捕获振荡信号而直接逻辑锁死。所以先依靠内建低速主控低频率运行,并在代码里检测外部晶振起振平稳后切权,这才是工业级的稳定思路。

中断控制 NVIC:它是一座孤立的塔嘛?

系统时钟准备完毕后,下一个大家常常不知所措的元件就是 NVIC (嵌套向量中断控制器)。

很多新手的疑问在于:如果我一个项目有串口、ADC,那我能不能把包含各种优先级的 NVIC_Init 全都堆在一个集中的函数里?

NVIC 与目标外设的生命羁绊

实际上,从架构设计来看,NVIC 虽然具有极高的全局控制权,配置的时候不该是“一次过包圆”的,它与外围设备的初始化强绑定在同一段代码中。

一条标准的功能初始化序列通常长这样:

- 系统时钟分配 (

RCC_APB2PeriphClockCmd送电外设网络) - GPIO 引脚分配 (挂载对应的引脚至备用复用模式或输入模式)

- 外设主功能初始化 (给 USART 设定波特率、将 DMA 设定源地址与目标地址)

- 👉为当前外设拉群组配中断 NVIC (

NVIC_IRQChannelCmd为该外设放行特定通道优先权) - 开启外设本尊最后生效 (

USART_Cmd(ENABLE))

这样的链式反应,意味着外设模块随时可以作为组件自由挂载与卸下,不污染全局;甚至由于代码执行时序问题,外设不配好,强行配置 NVIC 并打开也是存在乱中断抢占的越权风险的。

最后的总开关

当你把所有单独设备的 NVIC 通道均配置好优先级,打散绑定在它们各自的外设 init() 之后,唯一留在 main() 里面最末端的则是全局中断总闸。

如果忘开这个 __enable_irq();,抱歉,底下的 NVIC 全部沉默,不管你之前优先级设计得多么绝妙。

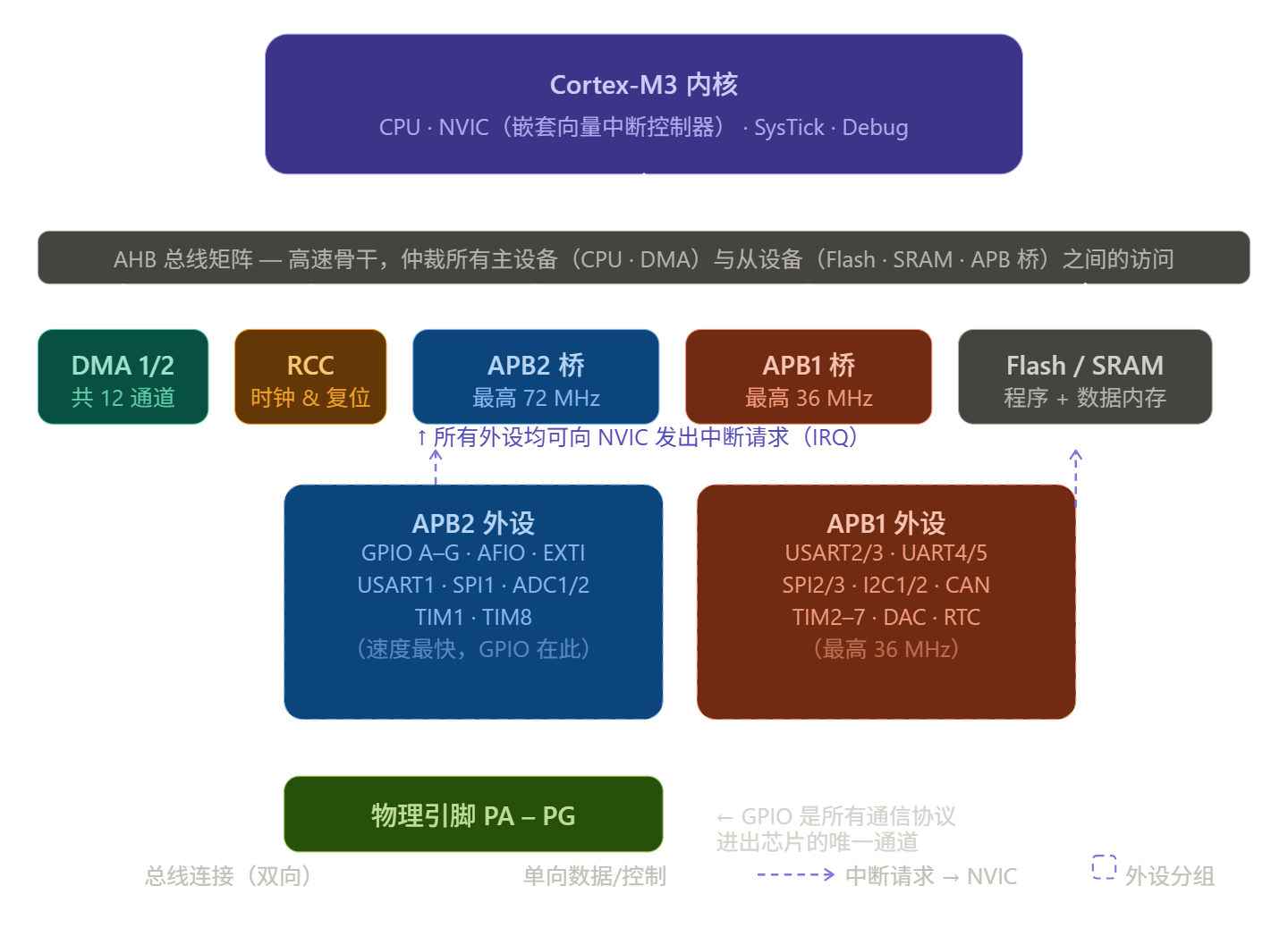

终极宏图:STM32F10xxx 数据流架构

在这些软件初始化的背后,支撑起如此多模块高并发工作的是位于核心舞台的 AHB 总线矩阵。

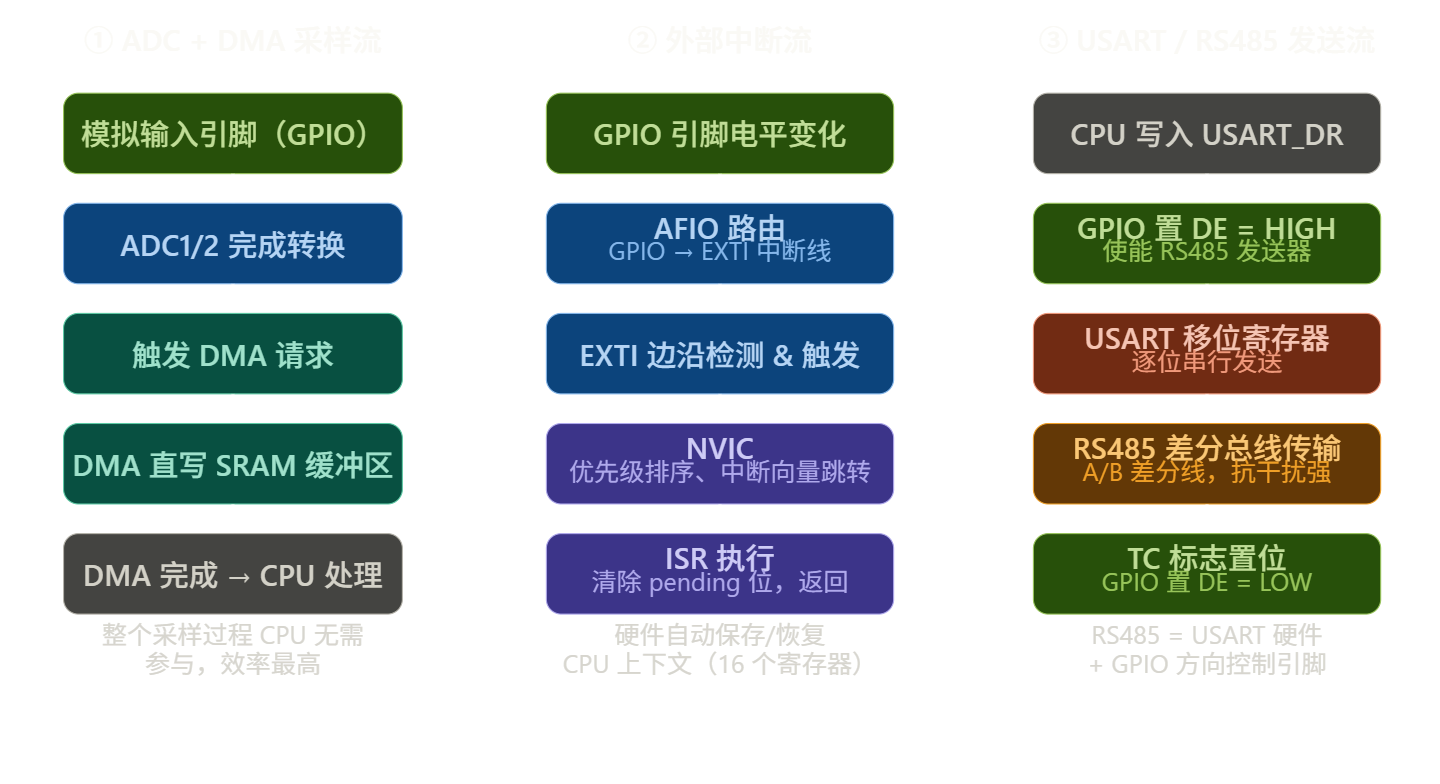

AHB 把 Cortex 核心、系统内存 (SRAM)、系统闪存 (Flash) 统统连接成一张网。而在它的身外散发出的,不仅有了 CPU 主导的执行流,还分支出 ADC 采样流 与 DMA 搬运流。 如果理解了上述 NVIC 和 时钟 的配置过程,你其实就是在一点点地、用软件开关的方式在这个巨型的开关阵列图中为你的业务搭桥铺路!